# **REVIEW ON IVY BRIDGE PROCESSOR**

# VIKASH KUMAR CHOUDHARY<sup>1</sup>, DEEPAK SHARMA<sup>2</sup> Dr Sanjay Kumar Bansal<sup>3</sup>

<sup>1</sup>Student, <sup>2</sup>Assistant professor<sup>3</sup> Dean FEA

<sup>1,2</sup>Department of ECE, PIET, Sitapura, Jaipur,<sup>3</sup>UCET Campus, Karni Industrial Area, Pugal Road, Bikaner-

# Abstract—

The last past few years of performance competition have become a greater competition method of improving processor performance. Moreover, it was not possible to use competition at the command level, and the problem of temperature reduction connected with larger multiplex microprocessors became a important problem. Though it is a multi-threaded approach was incorporated into the architectures of microprocessors to use directionlevel concurrency along to the appropriate level of instruction to enhance the microprocessor's execution ability. it stimulated the evolution of multi-core chip microprocessors. The present day research analyses the capabilities of Ivy Bridge microarchitectures to handle branching and stash instructions. this research of total microprocessors concerned were command to tests below in supervision of VTune tweeter application, which is used for research faulty sections predictions, caching errors, or relevant data collection.

## **1.INTRODUCTION**

The Past years of fibre synchronization have become a new method used together with the community at the instruction level to improve processor ability. This advanced idea of making more efficient multi core processors. Intel have used simultaneous multi strand called the hyper threading technique to boost the parallelism of its chips. One fibre will also be characterize a different action has own self-supported procedure of data and set of instruction. The vacant space of any dependencies generate the chips a improved destination for using similar things. In the multithreaded surroundings, the total enduring microprocessor. Here three type of different of class hardware highly threaded applications.

1.Multithreading of Fined Grain

The multithreading excellent grain, thin fibre will rotate in each loop to different the available function blocks, so that multiple threads are executed in an interconnected manner. The main improvement of this access of it. This will easily cover performance cost produce by memory delay. Although, the response this delays the activation of single fibres of microprocessor.

### 2.Multithreading of coarsed Grain

The multithreading of coarsed grain, texts individually changes as no event delays. The second is missing is the cache. Directions were given by another topic for using daughter circuits during this long latency events in microprocessor. This method has a greater disadvantage than others. Which tends to ignore minor latency events in microprocessor.

### 3. Simultaneous Multithreading

In simple manner of design advice can be provided from multiple threads to one threads. The key to this process is to make a similar type of multi processors units available to the concept of a developer. This uses a series of dynamic reorganization of all one to one and consistent instruction solutions. The rising technology is looking for developers and making them more sufficient by arranging in requirement as needed.

## **II. AECHITECTURE OF PROCESSOR**

### A. Microarchitecture of Intel Ivy Bridge Processor

This Bridge processor is an intel 22-nano meter microarchitecture based on the standard processor developed in 2011. This processor shows the microprocessor of intel third generation. It uses technique that was used in i7, i3 and i5 microprocessor. The IE7 and i3 computers supports communications technology and so each one of them can easily handles the two thread in paralleled manner. Both are represented as two values of while the

### Juni Khyat (UGC Care Group I Listed Journal)

bigger technology is used by suitable conditions. Additionally, Ivy microprocessor do support advanced vector extension(AVX) set of instructions.

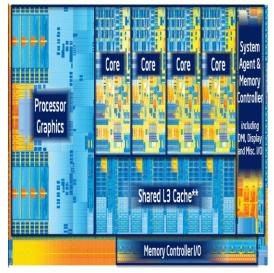

Fig 1. Architecture of Ivy Bridge Processor

# **B.** Predictors of Branch

The microarchitecture of Ivy bridge is a level two prediction tool that is used with 32 bit of global branches. It is different from previous generation of processors. This microarchitecture of chips least branches of approx. 15% of the duty cycle.

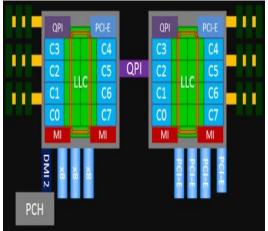

Fig 2. Branch predictors

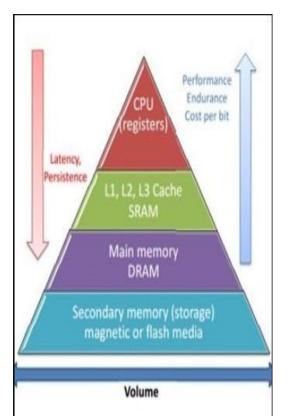

# 1. Hierarchy of Cache

Microarchitecture of Ivy bridge based microprocessor have cache levels of three steps. Early one contains the stash memory of (L1D). A logical Kernel, when a hyper threading technique is coming in effect shows the L1D stash memory data. And another level is L2. L2 or L1 stash memories are unique

## ISSN: 2278-4632 Vol-10 Issue-5 No. 9 May 2020

caches stash memory to individual kernel in microprocessor. And last is third one, which is called L3 or LLC shares with ring connection through the cores of

microprocessor. Table 1 describes the cache memory of the Ivy Bridge microarchitecture microprocessor.

|   | Level           | Potential of Chips | Load<br>delay      |

|---|-----------------|--------------------|--------------------|

| 1 | Class cache     | 32 KB              | No delay           |

| 2 | L1 cache memory | 32 KB              | 4                  |

| 3 | L2Cache memory  | 32 KB              | 12                 |

| 4 | L3 cache memory | differs            | differs(<br>26-31) |

TABLE I : CACHE POTENTIAL IN IVYBRIDGE MICROPROCESSOR

# III. TRIAL ENVIROMENT OR BASIS OF IVY

VTune tweeter of intel developed in 2018 software tool used to process the performance the microprocessor. Intel's i5 and i3 microprocessors used for run the tests according to intel's VTT tweeter of 2018 software tool. Table 3 shows the configuration of both the microprocessors.

### TABLE II: PROCESSOR SPECIFICATIONS

|   |                  | Core i3   | Core i5         |

|---|------------------|-----------|-----------------|

| 1 | Microarchitectur | Ivybridg  | Broadwell       |

|   | e                | e         |                 |

| 2 | Procedure Node   | 21.9nm    | 13.9nm          |

| 3 | CPU              | 3.9       | 3.98            |

|   | Count(Logical)   |           |                 |

| 4 | Frequencies      | 2.3Ghz    | 2.19Ghz         |

| 5 | Predictor of     | А         | Two             |

|   | Branches         | predictor | forecasters are |

|   |                  | which is  | used in         |

|   |                  | of level  | microprocesso   |

|   |                  | two.      | r. The fastest  |

|   |                  | Which is  | is related to   |

|   |                  | of global | the stash data  |

|   |                  | branch    | which is        |

|   |                  | of 32 bit | instruction     |

|   |                  | and       | data. And       |

|   |                  | barrier   | slower is with  |

|   |                  | table     | barrier target. |

## **Copyright © 2020 Authors**

### Juni Khyat (UGC Care Group I Listed Journal)

## ISSN: 2278-4632 Vol-10 Issue-5 No. 9 May 2020

The indicators show down, was used to process execution of each microprocessor.

A. CPI (Clock per instruction rate)-

The matrix represents task cycle numbers for each instruction set. This indicates the processor's execution in specific manner in seven times the number cycle.

B. Branch mispredict-

This matrix spoils some of the processor holes due to branch failures. When we use a misinformed branch by all phases used by these instructions will be destroyed.

C. Instructions caches(Icache)-

When receiving direct instructions from memory, the first level one cached is checked. If the study order is not found, it may cause an error.

D. Bound of Memory-

This metric shows how many times the machine was corrupted due to problems with memory subsystems. This calculates the portion of slots that were stopped because of demand or orders to store.

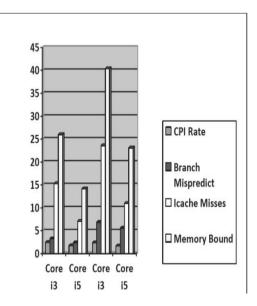

Fig 3. Memory Bound

Fig 4. Observation of Microprocessors

Fig 1 describes the graphical representation of the value entered during a core i5 and i3 microprocessor check for the different metrics evaluated by the Vtune tweeter software tool. This results describes that the core i5 microprocessor does not have a better CPI frequency, lower branch errors, ICH memory and memory problems for the two test cases.

## V. CONCLUSION

This result of this research confirm that, by branch free micro architecture low- branch misalignments are missing and the temporary storage showed better on i5 microprocessor. In addition the analysis of matrix evaluated by the intel Vtune leads to the conclusion that the microarchitecture Ivy bridge works with the intel core i5 microprocessor with the intel display.

### References-

[1] D. Levinthal, "Performance Analysis Guide for Intel Core i7 Processor and Intel Xeon 5500 Processors", Intel Performance Analysis Guide, 2009.

[2] "Hyper-Framing", encyclopedia.org, 2017. [Online Online]. Available: https://en.wikipedia.org/wiki/Hyper-threading. [Accessed: 23-Dec-2017].

# **Copyright © 2020 Authors**

### Juni Khyat (UGC Care Group I Listed Journal)

[3] D. Patterson and Jay. Hansi, Comp. Architecture Architecture. San Mateo, California: Morgan Koman Publishers, 1990.

[4] "List of Intel CPU Microarchitectures", NVikipedia.org, 2017. [Online Online]. Available: https://en.wikipedia.org/wiki/List\_of\_Intel\_CPU\_m icroarchitectures. [Accessed: 23-Dec-2017].

[5] "Ivy Bridge (Microarchitecture)", Enviki Wikipedia, 2017. [. Online]. Available: https://en.wikipedia.org/wiki/Ivy\_Bridge\_ (microarchitecture). [Accessed: 23-Dec-2017].

[8] Intel® 64 and IA-32 Architectures Optimization Reference Manual. Intel Corporation, 2016. Available:

# ISSN: 2278-4632 Vol-10 Issue-5 No. 9 May 2020

https://www.intel.com/content/dam/www/public/us /en/documents/manu als/64-ia-32-architecturesoptimization-manual.pdf

[9] "Broadwell (microarchitecture)", En.wikipedia.org, 2017. [Online]. Available: https://en.wikipedia.org/wiki/Broadwell\_(microarc hitecture). [Accessed: 23- Dec- 2017].

[10] J. Reinders, a key Vtune performance analyzer. California: Intel Press, 2007.

[11] L. Akyil, H. Bockhorst, G. Slavova and A. Supalov, "Using Intel® VTune <sup>™</sup> Amplifier XE for High Performance Calculations", 2011. Available: http://www.vihps.org/upload/ material / TW11 / VTune\_Amplifier\_XE\_MPI. pdf